【導(dǎo)讀】在芯片設(shè)計的精密體系中,復(fù)位信號本是保障功能啟動的“安全錨點”,但當(dāng)復(fù)位邏輯突破單一域的限制、跨越不同域邊界時,這個原本可靠的“錨點”卻可能演變?yōu)闈摬叵到y(tǒng)風(fēng)險的“隱形裂縫”。跨復(fù)位域(RDC)問題正是這樣一種隱蔽的挑戰(zhàn):它讓功能仿真顯示“一切正常”,卻在芯片回片后的復(fù)雜工況下,因復(fù)位信號的異步釋放、時序偏差等觸發(fā)隨機(jī)功能錯誤,輕則導(dǎo)致系統(tǒng)異常,重則造成流片失敗。對于追求高可靠性的現(xiàn)代芯片開發(fā)而言,建立一套可靠的RDC簽核流程是確保一次流片成功的關(guān)鍵。

核心概念:什么是復(fù)位域與RDC?

要理解RDC,首先要明確“復(fù)位域”的概念。復(fù)位域是指由同一個異步復(fù)位信號控制的一組寄存器或邏輯模塊。根據(jù)復(fù)位策略的復(fù)雜度,系統(tǒng)可以分為:

單復(fù)位域系統(tǒng):整個芯片使用一個全局復(fù)位信號,這是最簡單、理想的情況。

多復(fù)位域系統(tǒng):不同功能模塊(如CPU核心、DMA控制器、外設(shè))使用各自獨立控制的復(fù)位信號。這些信號可能異步釋放,也就是釋放時間不同、甚至來自不同的邏輯區(qū)塊或電源域。現(xiàn)代復(fù)雜的片上系統(tǒng)(SoC),從手機(jī)處理器到數(shù)據(jù)中心AI芯片,幾乎都是復(fù)雜的多復(fù)位域系統(tǒng)。

跨復(fù)位域(RDC),就是指一個信號從一個復(fù)位域傳輸?shù)搅硪粋€復(fù)位域的路徑。當(dāng)這兩個域的復(fù)位信號在類型、時序或相位關(guān)系上存在差異時,RDC風(fēng)險就產(chǎn)生了。

為何RDC是危險的“芯片殺手”?

RDC風(fēng)險容易被忽視,通常緣于復(fù)位網(wǎng)絡(luò)在大型設(shè)計中不像時鐘網(wǎng)絡(luò)那么復(fù)雜,設(shè)計者容易對此掉以輕心。然而其發(fā)生的后果與異步時鐘域交叉引起的后果同樣致命。RDC的核心風(fēng)險源于復(fù)位的異步性,寄存器的異步復(fù)位輸出由于缺乏時序上的約束,使得后續(xù)的時序電路可能引發(fā)一系列問題:

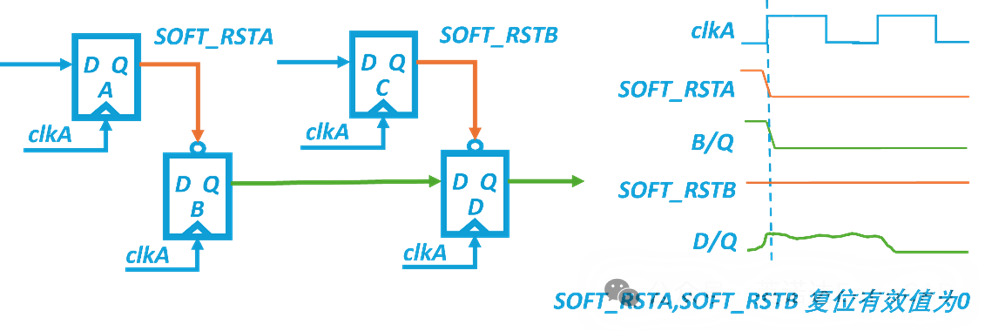

亞穩(wěn)態(tài)風(fēng)險:這是最經(jīng)典也最危險的問題。如果發(fā)送域的復(fù)位先激活,其輸出信號開始變化,而此時接收域的寄存器仍處于活躍狀態(tài),其時鐘沿可能恰好采到正在變化的信號,導(dǎo)致寄存器輸出陷入既非“0”又非“1”的亞穩(wěn)態(tài),并將這個不確定狀態(tài)傳播到后續(xù)電路,導(dǎo)致功能性錯誤。

復(fù)位毛刺傳播:如果異步復(fù)位信號由組合邏輯產(chǎn)生,復(fù)位信號可能由于組合邏輯不同輸入路徑延遲不同產(chǎn)生毛刺,從而對時序電路進(jìn)行未預(yù)期的復(fù)位,導(dǎo)致功能紊亂。

復(fù)位同步后的再匯聚問題:當(dāng)兩個源自相同復(fù)位域或不同步復(fù)位域的信號,經(jīng)過不同路徑(如不同長度的同步器鏈)同步到同一復(fù)位域后再次匯聚時,可能由于復(fù)位同步路徑上的延遲差異而失去數(shù)據(jù)上的關(guān)聯(lián)性,導(dǎo)致邏輯錯誤。

這些錯誤的隱蔽性極強(qiáng),傳統(tǒng)的驗證方法,如STA或常規(guī)的功能仿真,很難捕捉到它們,因為問題只在特定、罕見的復(fù)位時序組合下才會被觸發(fā)。 一旦帶有RDC問題的芯片流入市場,故障現(xiàn)象間歇性出現(xiàn),診斷和修復(fù)的成本極其高昂。

設(shè)計實踐:從源頭防范RDC

優(yōu)秀的芯片設(shè)計不僅依靠后期驗證,更在于前期的架構(gòu)規(guī)避。工程師們有一系列成熟的設(shè)計準(zhǔn)則來減少RDC風(fēng)險:

首要原則-復(fù)位架構(gòu)簡化:在系統(tǒng)架構(gòu)設(shè)計階段,應(yīng)盡量減少不必要的異步復(fù)位源。對于同一時鐘域內(nèi)的模塊,盡量使用同步復(fù)位或統(tǒng)一的異步復(fù)位,從根本上減少異步復(fù)位跨域路徑。

電路隔離與約束技術(shù):對于電路中存在從“異步復(fù)位中”信號到“未復(fù)位”信號的路徑,可以在路徑上插入復(fù)位隔離單元,在發(fā)送域復(fù)位有效期間將輸出鉗位到已知安全值。

復(fù)位機(jī)制保障:對于數(shù)據(jù)流確定的電路,通過電路設(shè)計保證上游電路先于下游電路復(fù)位,或者下游電路永遠(yuǎn)跟隨上游電路同時復(fù)位,這些復(fù)位機(jī)制能保證數(shù)據(jù)在跨復(fù)位域傳輸時消除風(fēng)險。

現(xiàn)代驗證利器:RDC專用簽核工具

即使遵循了最佳設(shè)計實踐,在數(shù)億門級規(guī)模的復(fù)雜芯片中,人工審查所有潛在的RDC路徑也是不可能的。這時,專業(yè)的RDC簽核工具就成為了保證流片成功的必備。英諾達(dá)EnAltius?跨域檢查工具,繼支持時鐘域交叉(CDC)檢查功能后,將進(jìn)一步推出RDC簽核檢查功能,幫助芯片開發(fā)者快速完成RDC的驗證和收斂。

總結(jié)

跨復(fù)位域問題體現(xiàn)了現(xiàn)代芯片設(shè)計中異步復(fù)位架構(gòu)的復(fù)雜性,行業(yè)內(nèi)的成功實踐表明,通過將前瞻性的復(fù)位架構(gòu)設(shè)計、系統(tǒng)性的復(fù)位場景管理,與強(qiáng)大的自動化簽核工具相結(jié)合,可以徹底地消除與復(fù)位相關(guān)的設(shè)計隱患。這不僅關(guān)乎工具的選擇,更關(guān)乎一套涵蓋設(shè)計、驗證和調(diào)試的完整方法論的建立。只有通過如此嚴(yán)謹(jǐn)縝密的流程,才能確保每一顆高度復(fù)雜的數(shù)字芯片都能穩(wěn)定、可靠地運行。